1. 레지스터 기본 구성

2. 마이크로 연산

= 마이크로 동작 = 마이크로 오퍼레이션 = μ-연산

- CPU에서 한 클럭 펄스 동안에 일어나는 세부 동작

- 레지스터 간 이루어지는 낮은 수준의 기본 동작

- 매크로 명령어 (여러개의 클럭 펄스 필요)

3. 레지스터 전송 언어 RTL

- Register Transfer Language

- 레지스터 동작을 기호로 나타낸 언어

- 어셈블리 언어의 중립적 형태

- 전송 & 연산과정 표시

| 기호 | 정의 |

| t₁ t₂ t₃ | 한 클럭 펄스 동안 일어나는 동작의 단계 |

| Y | 메모리 주소 Y |

| M[Y] | 메모리 주소 Y의 내용 |

| 레지스터 | 레지스터 내용 |

| M[레지스터] | 레지스터가 가라키는 내용 |

4. 상태 레지스터

= 플래그 레지스터 flag register

- 연산 결과에 따른 연산장치의 상태를 저장

- 최종 연산결과 상태에 따라 어느 플래그에 저장되는지 달짐

- 조건 분기 명령들 : 각 조건 플래그 비트의 상태에 따라 분기된다.

상태 레지스터 플래그 비트 세팅

| Z | E | C | S | O (V) | R | I | P |

| 제로 | 동등 | 캐리 | 부호 | 오버플로우 | 예비 | 인터럽트 마스크 | 권한 |

| 0이면 1 | 같으면 1 | 올림 있으면 1 | 양수면 0 음수면 1 |

오버되면 1 | 인터럽트 없으면 1 | 관리자면 1 |

5. 명령어 세트

- 특정 CPU를 위해 정의되는 명령어 리스트/집합

- 명령어 세트 구조 ISA, Instruction Set Architecture : 컴퓨터 구조의 일부

CPU 명령어 세트 설계 시, 고려사항

- 명령어 형식

- 주소지정방식

- 연산 종류

- 데이터 타입

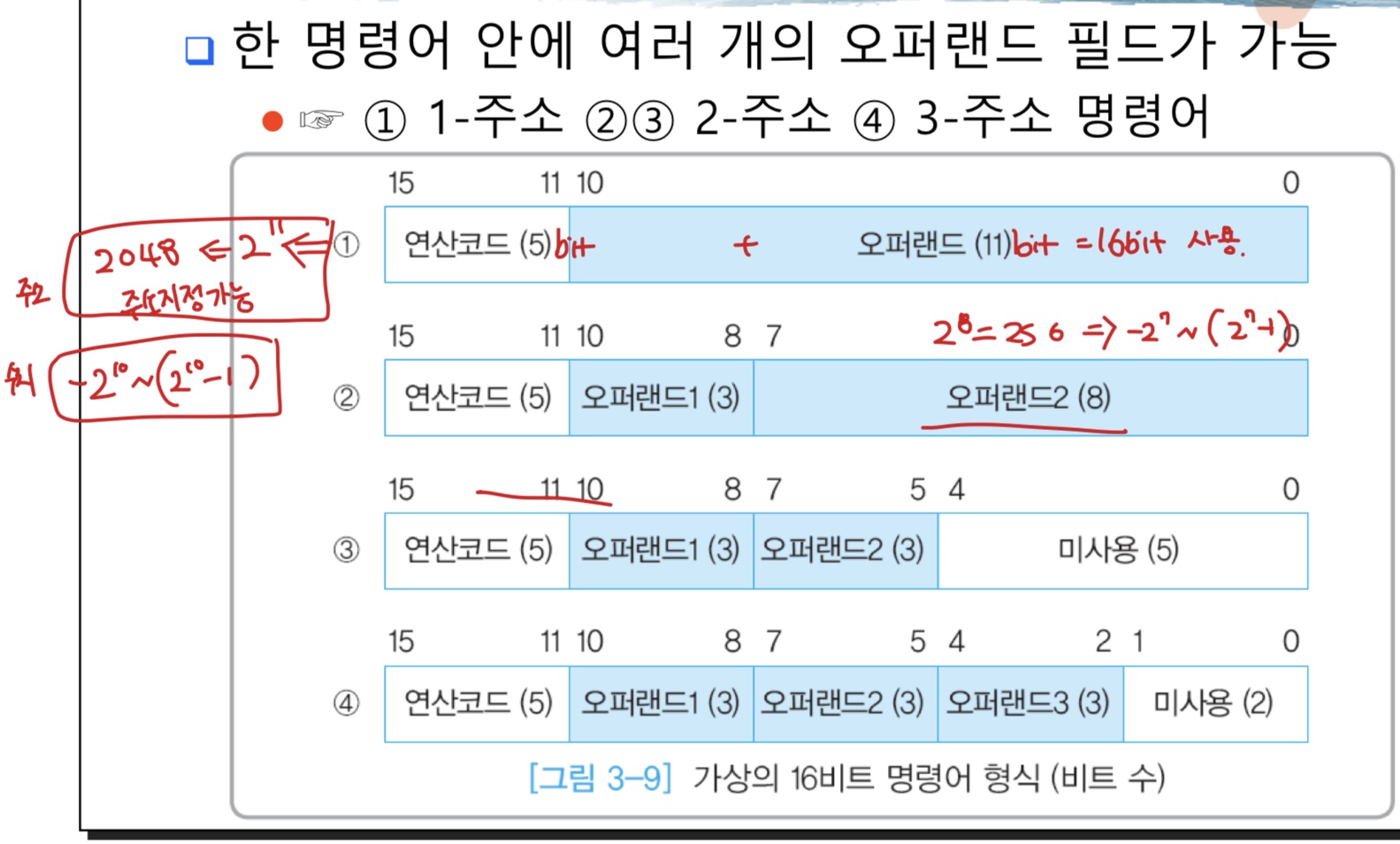

6. CPU 명령어 형식

- 명령어를 구성하는 비트를 여러 개의 필드로 나누어 정의한 것

- 연산코드 필드, 오퍼랜드 필드

- 필드 : 특정 데이터를 저장하도록 지정해 놓은 영역

7. 명령어 형식 설계 방법

8. 주소지정방식 종류 : 가상의 명령어 설계

어셈블리 명령어; 레지스터 전송 언어

암시적 Implied T = 0ns 메모리 접근 X

- 오퍼랜드(피연산자)없이

- 명령어 자체가 어떤 레지스터를 쓸지 암시한다.

- AC(누산기)를 기본 대상으로 한다.

** 오퍼랜드 없이 연산코드 자신만으로 특정 레지스터의 동작을 암시한다.

INC; AC ← AC + 1

즉치 Immediate T = 0ns 메모리 접근 X

- 오퍼랜드(피연산자) = 값

- 오퍼랜드 필드 안에 값이 직접 들어있음

** 명령어 형식의 오퍼랜드 필드에 " 즉시 사용할 수 있는 데이터 수치 "로 실제 피연산자가 들어있다.

ADD B, 90H; B ← B + 90H

직접 Direct T = 100ns 메모리 접근 1회

- 오퍼랜드(피연산자) = 유효주소(값이 저장된 메모리 주소)

** 오퍼랜드 필드에 '피연산자가 저장된 메모리 위치'인 유효주소가 들어있다.

ADD B, [1234H]; B ← B + M[1234H]

간접 Indirect T = 200ns 메모리 접근 2회

- 오퍼랜드(피연산자) = [ [메모리 주소가 저장된 장소]의 간접주소]

1. 간접주소 위치 읽기

2. 실제 주소로 접근

** 오퍼랜드 필드에 [유효주소의 주소]인 [간접주소]가 들어있다

ADD B, [[5678H]]; B ← B + M[ M[5678H]]

레지스터 Register T = 0ns 메모리 접근 1회

- 오퍼랜드(피연산자) = 레지스터(변수) 이름 자체

** 오퍼랜드 필드에서 지정한 레지스터에 피연산자

ADD B,C; B ← B + C

레지스터 간접 Register Indirect T = 0ns 메모리 접근 1회

- 오퍼랜드(피연산자) = 유효주소가 저장된 [레지스터]

** 오퍼랜드 필드에서 지정한 레지스터에 유효주소 저장

ADD B,[C]; B ← B + M[C]

상대 Relative T = 110ns 메모리 접근 1회 + 레지스터간 덧셈 1회

- PC + d(변위값)로 유효주소 계산

** 오퍼랜드 필드에서 지정한 PC에 저장된 장소 값과 변위값 d를 더해 유효주소 계산

ADD B, [PC+d]; B ← B + M[PC+d]

인덱스 Index T = 110ns 메모리 접근 1회 + 레지스터간 덧셈 1회

- IX + d로 주소 계산

** 상대 주소지정 방식의 일종으로, 인덱스 레지스터 IX를 별도로 사용하면 배열연산에 유리하다.

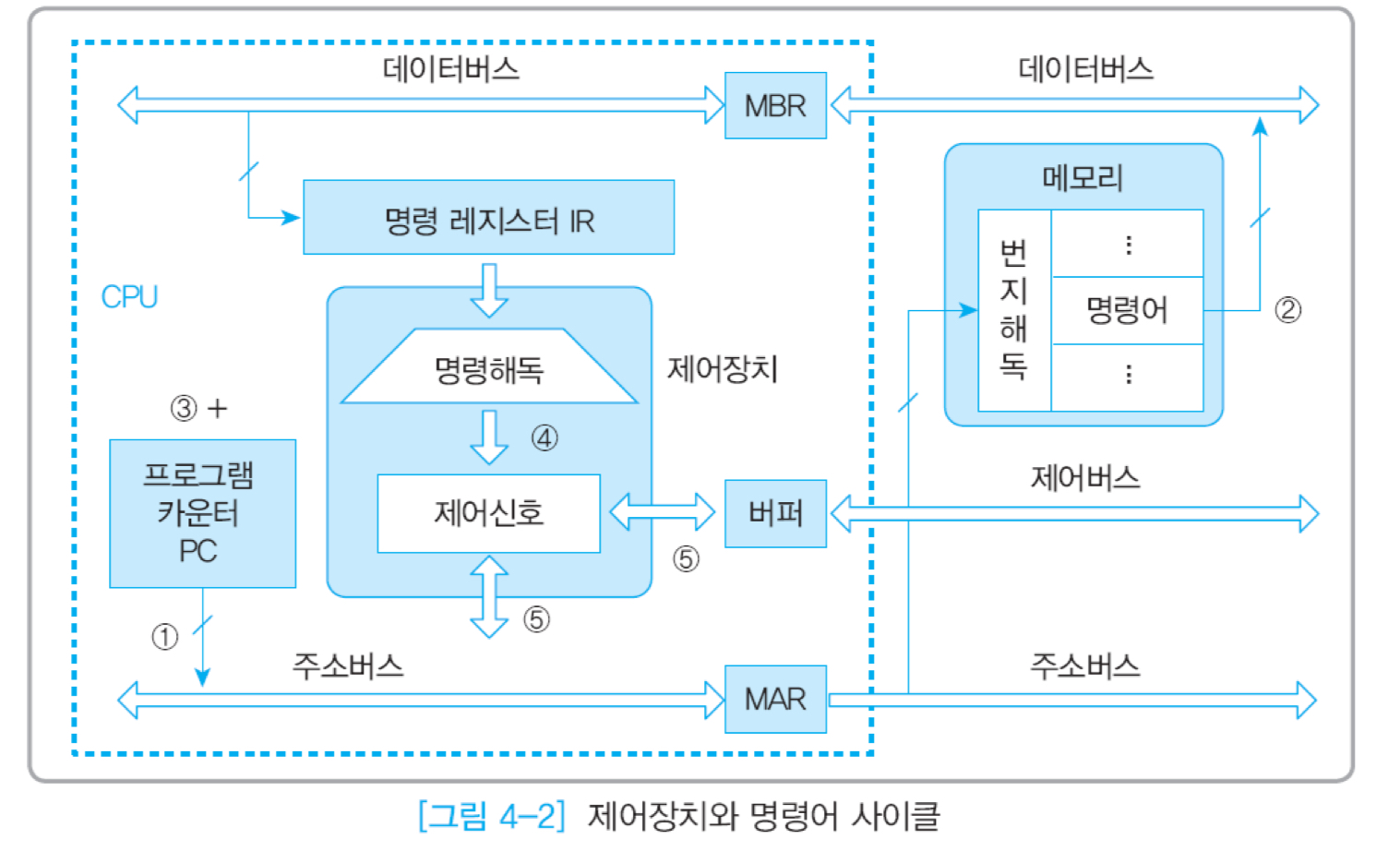

9. 제어장치와 명령어 사이클

- 명령어 인출, 해독 실행

- 명령어 기본 사이클 = 인출 사이클 + 실행 사이클

10. 스택 영역 LIFO

- 서브 루틴을 호출 할 때 메인 프로그램 의 이치로 다시 돌아올 복귀 주소를 메모리의 스택 영역에 저장해 놓음

- 스택 포인터 (SP) : CPU 레지스터 중 하나로, 현재 상태에서 이용 가능한 스택 영역의 최종 위치를 표시해줌

- 항상 스택영역의 최상위/최하위 주소를 가르킴

11. 다중 서브루틴과 스택 영역의 변화

12. 정수 산술 연산

정수 ➔ 2진수 ➔ -2진수 ➔ 1'c ➔ 2'c

-2진수 : 부호만 - 바꾸기

1'c : 0과 1 바꾸기

2'c : +1하기

13. IEEE754 표준 2진 부동소수점 수식 표현

- 음수 버전

- 양수 버전

| 1비트 부호 | 8비트 지수부 127 +- 지수 | 10110000000000000 19비트 |

14. 논리 연산

1. 마스크 연산 : AND

2. 선택적 연산 : OR

3. 삽입 연산 : AND 반, OR 반

4. 비교 연산 : XOR (다를때 1, 같을때 0)

5. 선택적 보수 연산 : XOR (원하는 위치의 비트만 1로 변경 ** 1은 1'c, 0은 0으로

15. 시프트 연산

1. 논리적 시프트 연산

| 0010 1101 | |||

| 왼쪽 논리 시프트 | 1011 0100 | 0000 1011 | 오른쪽 논리 시프트 |

| 왼쪽 기준 앞에 2개 없어짐 | 오른쪽 기준 앞에 2개 없어짐 | ||

2. 순환 시프트 연산

| 0010 1101 | |||

| 왼쪽 순환 시프트 | 0101 1010 | 1001 0110 | 오른쪽 순환 시프트 |

| 왼쪽 기준 맨 앞 숫자 뒤로 감 | 오른쪽 기준 맨 뒤 숫자 앞으로 감 | ||

3. 산술적 시프트 연산1

| 0010 1101 | |||

| 왼쪽 산술적 시프트 | 0001 0110 | 00101101 | 오른쪽 산술적 시프트 |

| 왼쪽 기준 앞에 2개 없어짐 | 오른쪽 기준 앞에 2개 없어짐 | ||

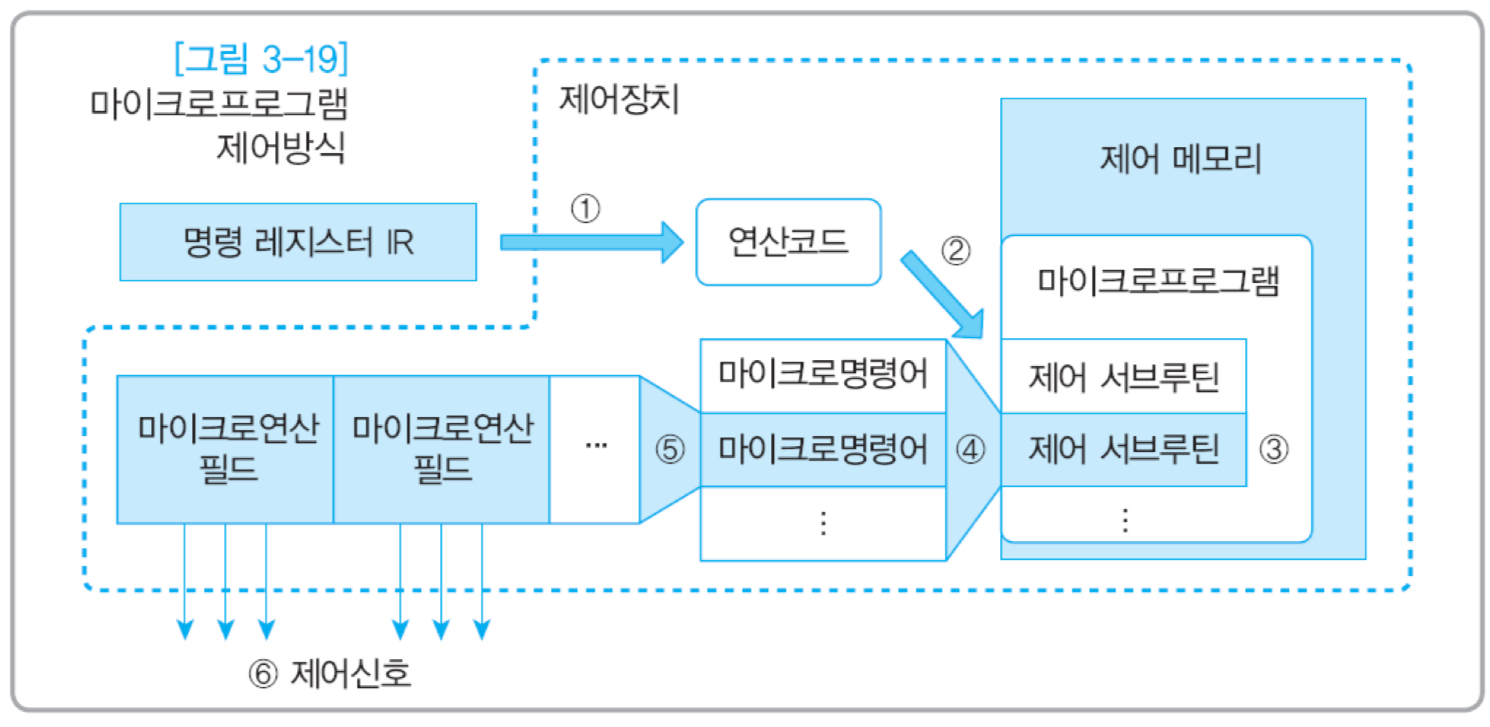

16. 마이크로 프로그래밍 제어 방식

- 제어 서브루틴 : 기계어 명령어 종류 하나를 처리한다.

- 제어신호를 발생시키는 마이크로 명령어들로 구성되어있음

1. 해독 : 명령 레지스터 IR에 들어온 명령어를 해독해 연산 코드 구함

2. 주소 계산 : 연산코드에서 해당 명령에 필요한 제어서브루틴의 시작주소를 계산함

3. 주소 찾기 : 제어 메모리의 마이크로 프로그램에서 제어 서브루틴을 찾는다

4. 인출 : 제어 서브루틴에서 마이크로 명령어를 차례대로 인출한다

5. 해독 & 결정 : 마이크로 명령어를 해독해 실행할 마이크로 연산 종류를 결정한다

6. 제어신호 출력 : 각 마이크로 연산 필드에서 제어신호를 만들어 출력한다.

17. 명령어 기본 사이클 = 인출 + 실행 사이클

- CPU 명령어 사이클 = 명령어 사이클 = CPU 사이클

- 프로그램에서 주어진 명령어를 실행하기 위해 반복적으로 수행하는 일련의 연속동작

18. 명령어 인출 사이클

- CPU가 메모리에서 명령어를 읽어오는 단계

- PC가 가르키는 메모리 내용에서 명령어를 순서대로 인출해 명령 레지스터 IR로 전송

주소 지정 → 꺼내옴 → 다음 준비

1. 명령어가 저장된 주소를 지정한다.

2. 해당 주소에 들어있는 명령어를 메모리에서 꺼내온다.

3. 다음번 명령어의 주소를 PC에 준비한다.

19. 명령어 실행 사이클

- CPU가 메모리에서 명령어를 수행하는 단계

- 명령 레지스터 IR에 저장된 명령어 해독하고, CPU 내외부에서 명령어 실행에 필요한 제어신호 발생

해독 → 실행 신호 발생

1. 명령어 해독

2. 명령어 실행에 필요한 CPU 내외부 제어신호 발생

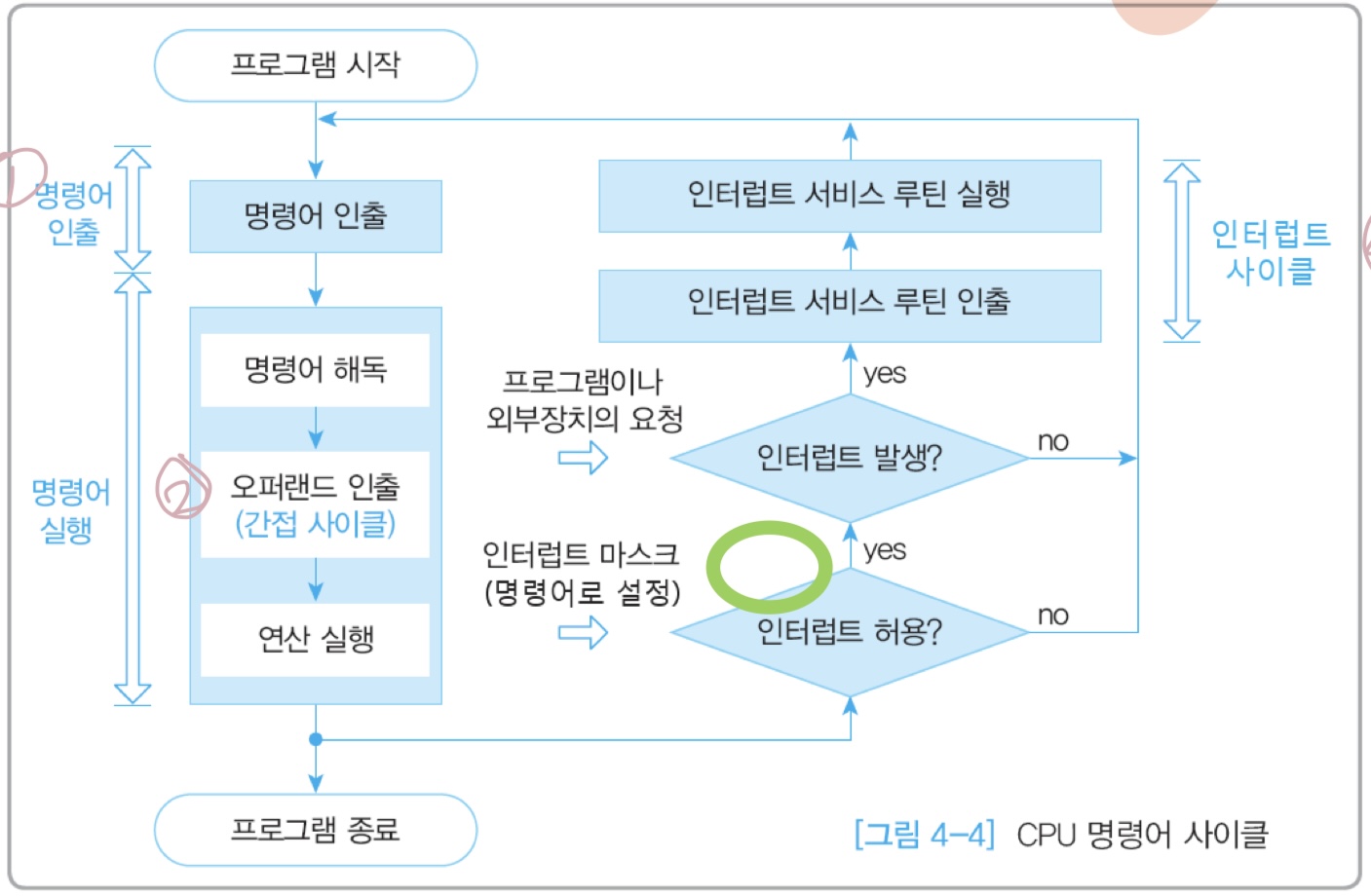

20. 인터럽트 사이클

- 프로그램의 정상 처리순서를 방해하는 서비스 요구

- CPU 외부장치 / 프로그램 요청에 의해 발생

ㄴ 하드웨어 인터럽트 : CPU 외부장치에서 발생

ㄴ 소프트웨어 인터럽트 : 프로그램 요청으로 발생

인터럽트 요구 수행시

1. CPU 작업 중단

2. 현재 상태 스택에 저장 ( 복귀주소, 레지스터 상태 등)

3. 인터럽트 서비스 루틴(= 핸들러) 실행하여 인터럽트 처리

4. 스택에 저장해둔 CPU 상태 복권

21. 다중 인터럽트

- 인터럽트 서비스 프로그램이 진행 도중 또 다른 인터럽트 발생 (= 다중 서브 루틴 개념)

인터럽트 마스크 / 마스킹 방법

- 인터럽트 발생 시, 받아들이지 않도록 금지 플래그 설정

ㄴ 인터럽트 불가능 설정 : 새로운 인터럽트 대기 시키기

ㄴ 인터럽트 가능 설정 : 새로운 인터럽트 수용

우선순위 방법

- 현재 작업보다 순위 높으면 시작

- 낮으면 대기

22. CPU 명령어 사이클

기본 사이클(인출, 실행) + 간접 사이클 + 인터럽트 사이클

CPU 명령어 사이클 처리 순서

1. 명령어 인출

2. 명령어 해독

3. 오퍼랜드 인출 (피연산자 데이터 가지고 오기)

4. 연산 실행📌 CPU 명령어 사이클 : 기본사이클 + 간접 사이클 + 인터럽트 사이클

1. 명령어 인출 : 메모리에서 명령어 읽고 CPU로 가져옴

2. 간접 사이클 : 오퍼랜드 필드의 간접주소에서 유효주소 읽음

3. 명령어 실행 : 명령어 해독 & 연산 실행

4. 인터럽트 사이클 : 인터럽트 요구에 해당하는 서비스 루틴 실행

'Basic > 컴퓨터구조' 카테고리의 다른 글

| 컴퓨터구조 기말고사 퀴즈 정리 (1) | 2025.12.05 |

|---|---|

| 컴퓨터구조 -1- (0) | 2025.10.20 |

| 컴퓨터구조 -1- 퀴즈 (0) | 2025.10.17 |